# 2 T836/837 Circuit Operation

This section provides a basic description of the circuit operation of the T836 transmitter and T837 exciter.

The following topics are covered in this section.

| Section |       | Title                             | Page |

|---------|-------|-----------------------------------|------|

| 2.1     |       | Introduction                      | 2.3  |

| 2.2     |       | Synthesiser                       | 2.4  |

| 2.3     |       | VCO                               | 2.6  |

|         | 2.3.1 | Two-Point Modulation              | 2.6  |

|         | 2.3.2 | VCO Supply                        | 2.6  |

| 2.4     |       | Audio Processor                   | 2.7  |

|         | 2.4.1 | General                           | 2.7  |

|         | 2.4.2 | Audio Inputs                      | 2.7  |

|         | 2.4.3 | Keying Inputs                     | 2.8  |

|         | 2.4.4 | Compressor                        | 2.8  |

|         | 2.4.5 | Outputs To Modulators             | 2.8  |

| 2.5     |       | Power Supply & Regulator Circuits | 2.9  |

| 2.6     |       | T836 Drive Amplifier & PA         | 2.10 |

| 2.7     |       | T837 Exciter Drive Amplifier      | 2.10 |

| Figure | Title                                           | Page |

|--------|-------------------------------------------------|------|

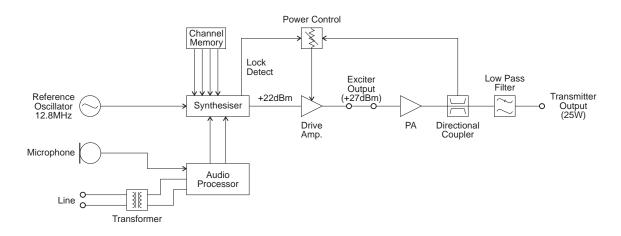

| 2.1    | T836 High Level Block Diagram                   | 2.3  |

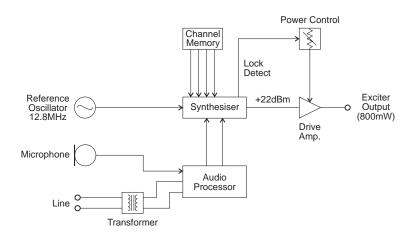

| 2.2    | T837 High Level Block Diagram                   | 2.3  |

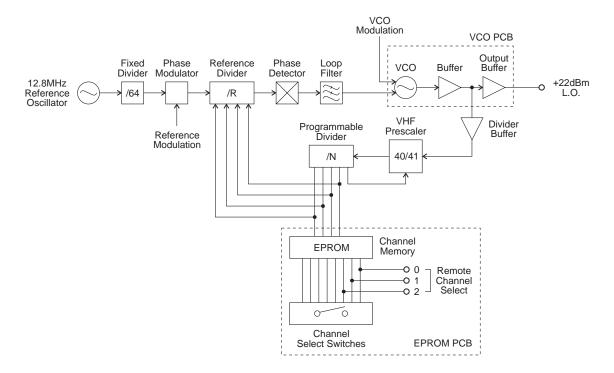

| 2.3    | T836/837 Synthesiser Block Diagram              | 2.5  |

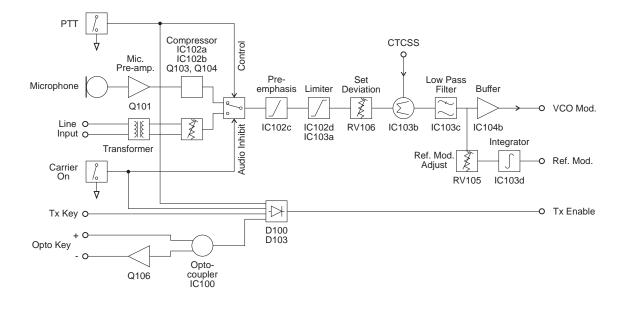

| 2.4    | T836/837 Audio Processor Block Diagram          | 2.7  |

| 2.5    | T836/837 Power Supply & Regulator Block Diagram | 2.9  |

# 2.1 Introduction

The individual circuit blocks which make up the T836 and T837 are:

- synthesiser

- VCO

- audio processor

- drive amplifier

- power amplifier (T836 only)

- voltage regulators.

Each of these circuit blocks is set in its own shielded compartment, formed as an integral part of the main chassis.

The configuration of the circuit blocks may be seen on a functional level in Figure 2.1 and Figure 2.2. Refer to the circuit diagrams for more detail.

Figure 2.1 T836 High Level Block Diagram

Figure 2.2 T837 High Level Block Diagram

### 2.2 Synthesiser

(Refer to Figure 2.3.)

The synthesiser employs a phase-locked loop (PLL) to lock a voltage controlled oscillator (VCO) to a given reference frequency. A reference oscillator at 12.8MHz (IC1) is buffered (IC7c & b) and divided down to 200kHz (IC4). This 200kHz square wave is then summed with the modulating audio and passed to an integrator (IC7f, Q8, Q9). This produces a ramping waveform which is centred around a DC level determined by the incoming audio. IC7e performs as a comparator, ultimately producing a phase-modulated 200kHz square wave. This is followed by a similar phase shifting stage (IC7d & a, Q10, Q11), before being divided down to 6.25kHz or 5kHz within the synthesiser IC (IC5).

A buffered output of the VCO is divided with a programmable divider, comprising a VHF prescaler (IC3) and a divider within IC5. This signal is compared with the phase modulated reference signal at the phase detectors in IC5. A digital phase detector (PDB) provides rapid coarse tuning of the VCO until the phase error is within the range of the high gain sample and hold detector (PDA). The phase detector outputs are passed through an active loop filter (IC6) which produces a DC voltage between 0V and 20V to tune the VCO. This VCO control line is further filtered to attenuate noise and other spurious signals. Note that the VCO frequency increases with increasing control voltage.

If the synthesiser loop loses lock, a pulsed signal appears at LD (pin 3) of IC5. This signal is filtered and buffered by IC6, producing the lock detect signal used to shut off the power supply to the drive amplifier.

The division ratio of the programmable divider is stored within EPROM memory. Up to 128 frequencies can be stored within the EPROM and are addressed using the internal DIP switches. Three of the address lines are also available for external frequency control via an extra D-range connector at the rear of the chassis. A change of state of any of these three lines commences a programming cycle, during which time the frequency data in the EPROM is down loaded to the divider (IC5). 32 bits of data are loaded in eight 4-bit words.

Note that the three address lines must change their state decisively and simultaneously. Methods which allow the states of the three lines during transition to be undefined for indeterminate lengths of time, as with some mechanical BCD switches, are unsuitable.

Figure 2.3 T836/837 Synthesiser Block Diagram

# 2.3 VCO

The VCO transistor (Q1) operates in a common source configuration, with an LC tank circuit coupled between its gate and drain to provide the feedback necessary for oscillation. The VCO control voltage from the loop filter (IC6) is applied to the varicaps (D1-D4) to facilitate tuning within an 8MHz band of frequencies. A trimcap (VC1) is used for coarse tuning of the VCO. The output from the oscillator circuit drives a cascode amplifier stage (Q2, Q3) which supplies +10dBm (typically) to a further stage of amplification, Q5. This is the final amplifier on the VCO PCB, and delivers +22dBm (typically) to the exciter drive amplifier.

A low level "sniff" is taken from the input to Q5 and used to drive the divider buffer for the VHF prescaler (IC3). The prescaler divide ratio is 40/41.

The VCO operates at the actual output frequency of the exciter, i.e. there are no multiplier stages. It is modulated by superimposing the audio signal onto the control voltage and by phase modulating the reference signal.

### 2.3.1 Two-Point Modulation

Both the VCO and reference oscillator are modulated so that the phase detectors of IC5 see no frequency error under modulation. Thus, the synthesiser loop will not attempt to correct for modulation and the response of the transmitter remains unaffected.

### 2.3.2 VCO Supply

The VCO is supplied with two switched supplies, Tx reg. and +9V rail under the control of the Tx reg. supply.

The VCO and buffer amplifier are supplied from the +9V switched supply by Q6 via the C multiplier (Q5, C34).

The output amplifier is supplied from Tx reg.

Figure 2.4 T836/837 Audio Processor Block Diagram

#### 2.4.1 General

The audio processor comprises several link selectable circuit blocks which may be configured in a variety of combinations to suit individual requirements. The pre-emphasis network and compressor may be linked individually or cascaded between either or both audio inputs and the limiter.

Refer to Section 3.3.1 for linking details.

#### 2.4.2 Audio Inputs

Two audio inputs are available: one from a 600 ohm balanced (or unbalanced) line, and the other from a local microphone. The microphone signal is passed first to a pre-amplifier (Q101) and ultimately to a multiplexer (IC101), but in between may pass through the compressor (depending on the linking details). The line transformer is also connected to the multiplexer and is disabled by the microphone PTT switch.

A third input for CTCSS tones is also provided.

### 2.4.3 Keying Inputs

There are four ways to key the exciter:

- pulling the Tx-key line low (pin 13 on the D-range connector at the rear of the set);

- pushing the "Carrier" button on the front panel this will inhibit all audio;

- using the PTT button on the local microphone, disabling audio from the line;

- via the opto-key inputs (pins 11 and 12 on the D-range connector) where electrical isolation is required. This features a constant current source (Q106) to ensure reliable activation of the opto-coupler (IC100) at low keying voltages.

#### 2.4.4 Compressor

The input signal is fed via a current controlled attenuator (Q103, Q104) to a high gain stage (IC102a) from which the output signal is taken. This signal is passed to a comparator (IC102b) which toggles whenever the audio signal exceeds a DC threshold determined by RV104. Thus, the comparator produces a square wave whose mark-space ratio is determined by the amplitude of the audio signal. This square wave pumps up the reservoir capacitor (C129) which controls the attenuator (Q103, Q104), thus completing the feedback loop.

The compression level is set by adjustment of the comparator threshold (RV104).

*Note:* Although the high dynamic range of the compressor allows the use of very low audio signal levels, such conditions will be accompanied by a degradation of the signal to noise ratio. Very low audio input levels should therefore be avoided where possible.

#### 2.4.5 Outputs To Modulators

The output signal from the limiter (IC102d, IC103a) is added to any incoming CTCSS tone at a summing amplifier (IC103b). The signal is then low pass filtered (IC103c) and split to supply the two modulators.

Since the VCO modulator is a true frequency modulator, its audio is simply buffered (IC104b). The reference modulator, however, is a phase modulator and its audio must first be integrated (IC103d).

It is vital that the audio levels to the modulators are accurately set, *relative to each other*. Hence the inclusion of level adjustment in the reference modulator path (RV105). Once set, adjustments to absolute deviation may be made only via the deviation pot (RV106).

### 2.5 Power Supply & Regulator Circuits

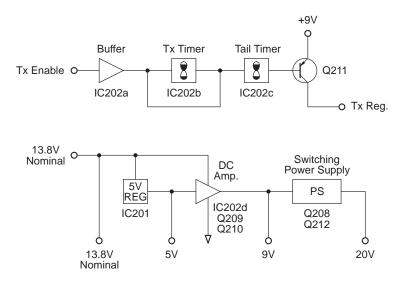

Figure 2.5 T836/837 Power Supply & Regulator Block Diagram

The T836 and T837 are designed to operate from a 10.8-16V DC supply, although the standard test voltage is 13.8V. A 5.3V regulator (IC201) running directly from the 13.8V rail drives much of the synthesiser circuitry. It is also used as the reference for a DC amplifier (IC202d, Q209, Q210) which provides a medium current capability 9V supply.

A self-oscillating, switching power supply (Q208, Q212) runs from the 9V supply, producing a low current capability +20V supply. This is used to supply the synthesiser loop filter (IC6), giving a VCO control voltage range of up to 20V.

Ultimate control of the transmitter is via the Tx reg. supply, switched from 9V by Q211. This is enabled by the Tx enable signal from the audio processor, but is subject to gating by the transmit timer (IC202b). If the transmitter is keyed continuously for a time exceeding that set by RV201 and C222, the Tx timer will force the Tx reg. supply off until the transmitter is keyed again. If required, the Tx timer may be disabled by removing R257.

The tail timer provides a repeater tail of up to several seconds and is adjusted by RV202.

# 2.6 T836 Drive Amplifier & PA

(Refer to Figure 2.1.)

A two-stage, wide band amplifier (Q300, Q301) provides an output level of approximately 500mW (+27dBm) for an input of 170mW (+22dBm) from the VCO. An 11V zener (D351) on the supply of IC350 provides a 10.5V regulated rail for the exciter.

To reduce the spurious output level the synthesiser out-of-lock signal inhibits the exciter via Q350 and IC350a.

R300, R301 and R302 form a 6dB attenuator to provide good VCO/exciter isolation.

The output attenuator (&R425, &R426, &R427 and &R428) aids in reducing exciter/PA interaction while also ensuring a reasonable match for Q301.

The RF output from the exciter is fed to the driver stage (&Q423) and then to the final (&Q424). DC is fed to the final via a low pass filter with special low frequency decoupling. &CV400 tunes the output matching across the entire band.

The directional coupler provides the required feedback for the power control loop while harmonics are attenuated by the low pass filter.

## 2.7 T837 Exciter Drive Amplifier

(Refer to Figure 2.2.)

A two-stage, wide band amplifier (Q300, Q301) provides an output level of approximately 800mW (+29dBm) for an input of 170mW (+22dBm) from the VCO. D351 (11V zener) on the supply of IC350 provides a 10.5V regulated rail for the exciter.

To reduce the spurious output level, the synthesiser out-of-lock signal inhibits the exciter via Q350 & IC350A.

R300, R301 & R302 form a 6dB attenuator to provide good VCO/drive amplifier isolation.

The output attenuator (&R425, &R426, &R427, &R428) assists in reducing exciter/PA interaction while also ensuring a good match for Q301.